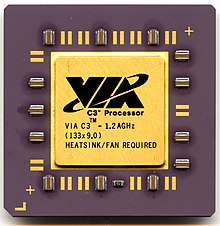

VIA C3

|

|

| Produced | 2001 |

|---|---|

| Common manufacturer(s) |

|

| Max. CPU clock rate | 500 MHz to 1.4 GHz |

| FSB speeds | 100 MHz to 133 MHz |

| Min. feature size | 0.13 to 0.15 |

| Instruction set | x86 |

| Socket(s) |

|

| Core name(s) |

|

The VIA C3 is a family of x86 central processing units for personal computers designed by Centaur Technology and sold by VIA Technologies. The different CPU cores are built following the design methodology of Centaur Technology.

VIA Cyrix III was renamed VIA C3 with the switch to the advanced "Samuel 2" (C5B) core. The addition of an on-die L2 cache improved performance somewhat. As it was not built upon Cyrix technology at all, the new name was just a logical step. To improve power consumption and reduce manufacturing costs, Samuel 2 was produced with 150 nm process technology.

The VIA C3 processor continued an emphasis on minimizing power consumption with the next die shrink to a mixed 130/150 nm process. "Ezra" (C5C) and "Ezra-T" (C5N) were only new revisions of the "Samuel 2" core with some minor modifications to the bus protocol of "Ezra-T" to match compatibility with Intel's Pentium III "Tualatin" cores. VIA enjoyed the lowest power usage in the x86 CPU market for several years. Performance, however, fell behind due to the lack of improvements to the design.

Uniquely, the retail C3 CPU shipped inside a metal package.

The "Nehemiah" (C5XL) was a major core revision. At the time, VIA's marketing efforts did not fully reflect the changes that had taken place. The company addressed numerous design shortcomings of the older cores, including the half-speed FPU. The number of pipeline stages was increased from 12 to 16, to allow for continued increases in clock speed. Additionally, it implemented the cmov instruction, making it a 686-class processor. The Linux kernel refers to this core as the C3-2. It also removes 3DNow! instructions in favour of implementing SSE. However, it was still based upon the aging Socket 370, running the single data rate front side bus at just 133 MHz.

Because the embedded system marketplace prefers low-power, low-cost CPU designs, VIA began targeting this segment more aggressively because the C3 fit those traits rather well. Centaur Technology concentrated on adding features attractive to the embedded marketplace. An example built into the first "Nehemiah" (C5XL) core were the twin hardware random number generators. (These generators are erroneously called “quantum-based” in VIA's marketing literature. Detailed analysis of the generator makes it clear that the source of randomness is thermal, not quantum.)

...

Wikipedia