Haswell (microarchitecture)

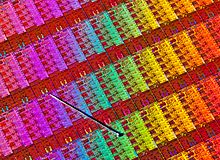

A Haswell wafer with a pin for scale

|

|

| CPUID code | 0306C3h |

|---|---|

| Product code |

|

| Cores |

|

| L1 cache | 64 KB per core |

| L2 cache | 256 KB per core |

| L3 cache | 2–40 MB (shared) |

| L4 cache | 128 MB of eDRAM (Iris Pro models only) |

| Model |

|

| Created | 2013 |

| Transistors | 22 nm (Tri-Gate) |

| Architecture | Haswell x86 |

| Instructions | MMX, AES-NI, CLMUL, FMA3 |

| Extensions | |

| Socket(s) |

|

| Predecessor | Ivy Bridge (Tick) |

| Successor | Broadwell (Tock/Process) |

| GPU |

|

| Brand name(s) |

|

Haswell is the codename for a processor microarchitecture developed by Intel as the "fourth-generation core" successor to the Ivy Bridge microarchitecture. Intel officially announced CPUs based on this microarchitecture on June 4, 2013 at Computex Taipei 2013, while a working Haswell chip was demonstrated at the 2011 Intel Developer Forum. With Haswell, which uses a 22 nm process, Intel also introduced low-power processors designed for convertible or "hybrid" ultrabooks, designated by the "Y" suffix.

Haswell CPUs are used in conjunction with the Intel 8 Series chipsets, Intel 9 Series chipsets, and Intel C220 series chipsets.

The Haswell architecture is specifically designed to optimize the power savings and performance benefits from the move to FinFET (non-planar, "3D") transistors on the improved 22 nm process node.

Haswell has been launched in three major forms:

Compared to Ivy Bridge:

Around the middle of 2014, Intel released a refresh of Haswell, simply titled Haswell Refresh. When compared to the original Haswell CPUs lineup, Haswell Refresh CPUs offer a modest increase in clock frequencies. Haswell Refresh CPUs are supported by Intel's new 9 Series chipsets (Z97 and H97, codenamed Wildcat Point), while motherboards with 8 Series chipsets (codenamed Lynx Point) usually require a BIOS update to support Haswell Refresh CPUs.

The CPUs codenamed Devil's Canyon, covering the i5 and i7 K-series , employ a new and improved thermal interface material (TIM) called next-generation polymer thermal interface material (NGPTIM). This improved TIM reduces the CPU's operating temperatures and improves the overclocking potential, as something that had been problematic since the introduction of Ivy Bridge. Other changes for the Devil's Canyon CPUs include a TDP increase to 88 W, additional decoupling capacitors to help smooth out the outputs from the fully integrated voltage regulator (FIVR), and support for the VT-d that was previously limited to non-K-series SKUs.TSX was another feature brought over from the non-K-series SKUs, until August 2014 when a microcode update disabled TSX due to a bug that was discovered in its implementation.

...

Wikipedia