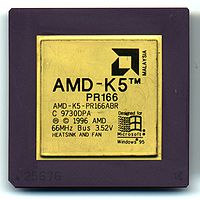

AMD K5

An AMD K5 PR166 microprocessor

|

|

| Produced | March 27, 1996 (SSA/5) October 7, 1996 (5k86) |

|---|---|

| Max. CPU clock rate | 75 MHz to 133 MHz |

| FSB speeds | 50 MHz to 66 MHz |

| Instruction set | IA-32/x86 |

| Microarchitecture | K5 |

| Cores | 1 |

| L1 cache | 8 KB + 16 KB (Data + Instructions) |

| Model | SSA/5 Series |

| Socket(s) | |

| Predecessor | Am5x86 |

| Successor | K6 |

The K5 is AMD's first x86 processor to be developed entirely in-house. Introduced in March 1996, its primary competition was Intel's Pentium microprocessor. The K5 was an ambitious design, closer to a Pentium Pro than a Pentium regarding technical solutions and internal architecture. However, the final product was closer to the Pentium regarding performance, although faster clock for clock compared to the Pentium.

The K5 was based upon an internal highly parallel 29k RISC processor architecture with an x86 decoding front-end. The K5 offered good x86 compatibility. All models had 4.3 million transistors, with five integer units that could process instructions out of order and one floating point unit. The branch target buffer was four times the size of the Pentium's and register renaming improved parallel performance of the pipelines. The chip's speculative execution of instructions reduced pipeline stalls. It had a 16 KB, four-way set associative instruction cache and an 8 KB data cache. The K5 lacked MMX instructions, which Intel started offering in its Pentium MMX processors that were launched in early 1997.

The K5 project represented an early chance for AMD to take technical leadership from Intel. Although the chip addressed the right design concepts, the actual engineering implementation had its issues. The low clock rates were, in part, due to AMD's limitations as a "cutting edge" manufacturing company at the time, in part due to the design itself (many levels of logic for the process technology of the day, hampering clock scaling). Having a branch prediction unit four times the size of the Pentium, yet reportedly not delivering superior performance is an example of how the actual implementation fell short of the project's goals. Additionally, while the K5's floating point performance was better than that of the Cyrix 6x86, it was weaker than that of the Pentium. Because it was late to market and did not meet performance expectations, the K5 never gained the acceptance among large computer manufacturers that the Am486 and AMD K6 enjoyed.

...

Wikipedia